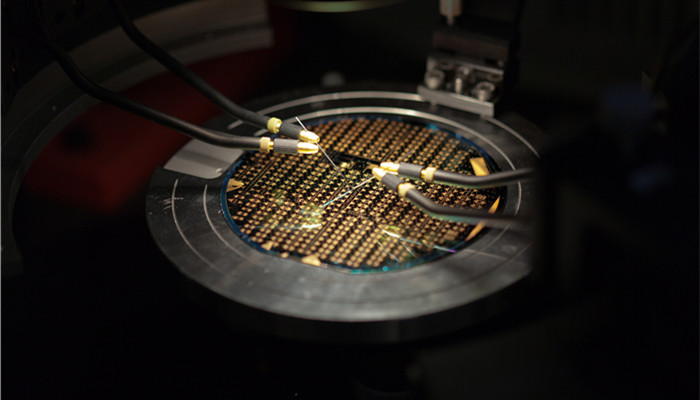

CFET,互补场效应晶体管,是一种新型的三维结构晶体管工艺,是在GAAFET工艺基础上改进得到,可理解为将两个独立的、具有不同导电沟道的GAAFET(p型和n型)在垂直方向上进行三维叠加,从而突破二维晶体管的性能与尺寸限制。CFET可以应用在2nm及以下更先进的工艺制程芯片制造中。

集成电路的设计遵循摩尔定律,每约18个月集成电路上的晶体管数量会增加一倍,这就要求晶体管的尺寸减小一半,而性能提升。随着芯片工艺制程不断进步,尺寸更小、功能更强大的晶体管工艺迭代速度加快,其技术升级的重点在于提升静电性能、控制漏电流。22nm芯片时代,FinFET取代MOSFE工艺,3nm芯片时代,GAAFET取代FinFET工艺,进入2nm芯片时代,CFET将取代GAAFET工艺。

根据新思界产业研究中心发布的

《2022-2027年中国CFET(互补场效应晶体管)行业市场深度调研及发展前景预测报告》显示,随着芯片工艺制程不断缩小,CFET概念被提出,这是当前最新一代晶体管工艺。CFET是在GAAFET工艺的基础上发展而来。GAAFET有两种结构,分别是纳米线(Nanowire)结构、纳米片(Nanosheet)结构。CFET一般采用Nanosheet结构,将一个p型Nanosheet FET叠加在一个n型Nanosheet FET之上,形成三维晶体管,可以显著增强晶体管性能,并减小其尺寸。

CFET制造工艺包括单片(monolithic)与顺序(sequential)两种。单片CFET先生长底部通道,然后沉积中间牺牲层,最后生长顶部沟道;顺序CFET是从底部向上制造元件,利用晶圆键合技术,在顶部覆盖一层半导体层,对顶部元件进行集成,并连接顶栅和底栅。对比来看,两种产品各有优缺点,单片CFET整合流程复杂,但成本较低,顺序CFET整合流程相对简单,但晶圆转移难度高。

新思界

行业分析人士表示,目前,CFET工艺仍在研究探索过程中,两种制造工艺哪一种更具发展价值尚未定论。虽然CFET适用于2nm及以下工艺制程芯片中,但从实际应用来看,2nm芯片仍可采用技术相对成熟GAAFET工艺,CFET在1nm芯片中更有应用价值。当前,半导体巨头台积电已经实现5nm芯片量产,3nm芯片计划2022年9月量产、2023年稳定量产,2nm芯片计划于2025年量产。由此来看,CFET虽然前景广阔,但目前商业化应用距离依然较远。

我国芯片研制能力较弱,为避免被“卡脖子”,相关工艺技术研究力度不断加大,CFET在先进工艺制程芯片制造中具有巨大潜力,中国科学院、北京大学等纷纷加入。2022年7月,中国科学院微电子研究所集成电路先导工艺研发中心团队,提出了新型混合沟道CFET(HC-CFET)结构设计和集成方案,其工作频率更高、噪声容限窗口更优。这有助于推动我国芯片行业核心竞争力不断增强。

关键字: